集成電路對講機 電路圖解析與集成電路設計探析

對講機作為一種重要的近距離雙向通信工具,其核心已經從早期的分立元件逐步演進為高度集成的集成電路(IC)方案。集成電路設計不僅極大地縮小了對講機的體積、降低了功耗,還顯著提升了其穩定性和功能豐富性。本文將從電路圖解析入手,深入探討對講機中集成電路的設計原理與關鍵技術。

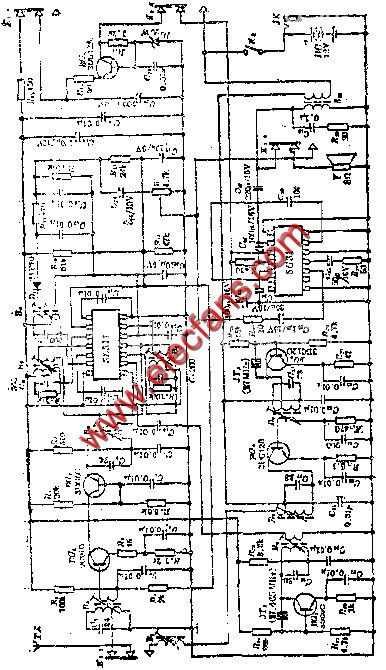

一、 經典集成電路對講機電路圖核心模塊解析

一套完整的對講機電路系統,其核心通常由一塊或幾塊專用集成電路構成。一個典型的單工調頻(FM)對講機電路圖主要包含以下幾個由IC實現的核心模塊:

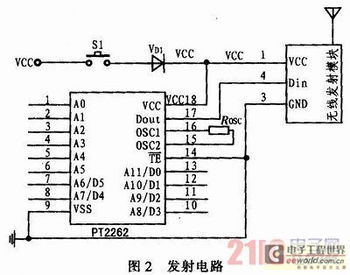

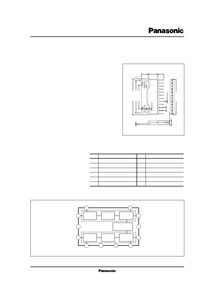

- 射頻收發模塊:這是對講機的“心臟”。現代對講機通常采用一顆集成了鎖相環(PLL)頻率合成器、壓控振蕩器(VCO)、混頻器、中頻放大器甚至功率放大器(PA)的射頻IC。在電路圖中,它連接著晶體振蕩器、環路濾波器、天線開關等外圍元件,共同完成載波頻率的精準生成、信號的調制與解調。

- 基帶/音頻處理模塊:負責語音信號的加工。發射時,麥克風拾取的微弱音頻信號經過運算放大器IC構成的預放電路后,送入調制器;接收時,從中頻IC解調出的音頻信號,需經過由音頻功率放大器IC驅動的揚聲器還原為聲音。靜噪電路、音頻濾波等也常由運放IC實現。

- 微控制器(MCU)模塊:在智能對講機中,一顆MCU是控制中樞。它在電路圖中連接著鍵盤、液晶顯示屏(LCD)、頻道選擇開關、PTT(按鍵通話)鍵等。MCU通過編程,管理著頻率設定、信道掃描、電池監測、數字信令(如CTCSS/DCS亞音編解碼)等所有邏輯與控制功能。

- 電源管理模塊:由低壓差線性穩壓器(LDO)IC或開關穩壓器IC構成,為射頻、基帶和MCU等不同模塊提供穩定、純凈且不同電壓等級的電源,確保系統高效、可靠工作。

通過分析電路圖,可以清晰地看到各IC之間的信號流向、電源分配及控制關系,這是理解對講機工作原理和進行故障排查的基礎。

二、 對講機專用集成電路的設計考量與挑戰

設計一款用于對講機的集成電路,工程師需要綜合考慮性能、功耗、成本與集成度,面臨多方面的技術挑戰:

- 射頻性能優化:射頻IC的設計是重中之重。需要在特定頻段(如VHF 136-174 MHz, UHF 400-470 MHz)實現低相位噪聲的頻率合成、高線性度的功率放大以及高靈敏度的低噪聲放大。這涉及到深亞微米射頻CMOS或SiGe BiCMOS工藝的選擇、片上電感與變壓器的優化設計,以在芯片面積和性能間取得平衡。

- 低功耗設計:對講機通常由電池供電,續航能力是關鍵。設計時需采用多電源域、時鐘門控、電源關斷等動態功耗管理技術。特別是在接收待機狀態,要使大部分電路處于極低功耗的“睡眠”模式,僅維持必要功能的運行。

- 高集成度與系統級封裝(SiP):為了追求極致的體積與成本優勢,趨勢是將射頻收發、基帶處理甚至MCU內核集成到單顆芯片上,即“單片對講機解決方案”。數字電路與敏感的模擬射頻電路集成會帶來嚴重的噪聲耦合問題。因此,精心的版圖布局、電源地隔離、襯底噪聲抑制技術至關重要。作為替代或補充,采用SiP技術將多顆不同工藝的裸芯片封裝在一起,也是實現高性能、小型化的有效途徑。

- 可靠性與穩定性:對講機工作環境復雜,IC必須具有良好的抗靜電(ESD)能力、寬工作溫度范圍以及穩定的頻率特性。在電路設計中需要加入完善的保護電路,并在制造工藝上予以保證。

- 支持靈活的可編程性:為了適應全球不同地區的頻率規劃與通信標準,現代對講機IC往往設計成可通過MCU軟件靈活配置頻率、調制偏差、亞音碼等參數,這要求IC內部有相應的可編程寄存器接口(如SPI、I2C)。

三、 未來發展趨勢

隨著物聯網和專用移動無線電的發展,對講機集成電路正朝著軟件定義無線電(SDR)方向演進。未來的對講機核心芯片可能是一個高度可編程的射頻前端配合一個強大的數字信號處理器(DSP),通過軟件實現波形、協議和功能的動態重構,從而實現更寬的頻帶覆蓋、更強的抗干擾能力和更豐富的增值服務。

一張簡潔的對講機電路圖背后,凝聚著精密的集成電路設計智慧。從模塊解析到芯片設計,每一步都體現了在有限資源下對通信性能、功耗與成本的不懈追求。理解這些,不僅能更好地應用和維護對講機設備,也為通信電子產品的創新設計提供了寶貴的思路。

如若轉載,請注明出處:http://www.cacacrc.org.cn/product/23.html

更新時間:2026-03-09 06:55:51