數(shù)字集成電路版圖設(shè)計入門 基于Cadence IC的原理圖繪制與仿真

一、 引言:從概念到物理實現(xiàn)

數(shù)字集成電路(IC)是現(xiàn)代電子系統(tǒng)的核心,從智能手機到數(shù)據(jù)中心,無處不在。其設(shè)計是一個復(fù)雜而精密的過程,通常從高層架構(gòu)描述開始,最終落實到硅片上的物理版圖。版圖設(shè)計(Layout Design)是連接電路邏輯功能與物理制造的關(guān)鍵橋梁。它決定了芯片的性能、功耗、面積和可靠性。本篇文章將聚焦于數(shù)字IC設(shè)計流程的前端關(guān)鍵環(huán)節(jié)——使用業(yè)界標(biāo)準(zhǔn)工具Cadence IC進行原理圖繪制與電路仿真,這是邁向成功版圖設(shè)計的第一步。

二、 Cadence IC設(shè)計平臺概述

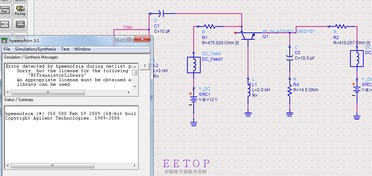

Cadence Design Systems 提供的集成電路設(shè)計平臺是行業(yè)內(nèi)的黃金標(biāo)準(zhǔn)之一。其集成環(huán)境(如Virtuoso)為模擬、混合信號及數(shù)字定制化設(shè)計提供了從原理圖輸入、電路仿真、版圖設(shè)計到物理驗證的完整解決方案。對于初學(xué)者和工程師而言,掌握Cadence IC的原理圖編輯器和仿真工具是進入IC設(shè)計領(lǐng)域的必備技能。

三、 原理圖繪制:構(gòu)建電路藍(lán)圖

原理圖(Schematic)是電路的圖形化表示,它使用符號來代表晶體管、電阻、電容、邏輯門等元器件,并通過連線定義它們之間的電氣連接。

- 設(shè)計啟動:在Cadence Virtuoso環(huán)境中,首先需要建立或打開一個設(shè)計庫(Library)和單元視圖(Cell View)。選擇創(chuàng)建“Schematic”視圖,即可進入原理圖編輯器。

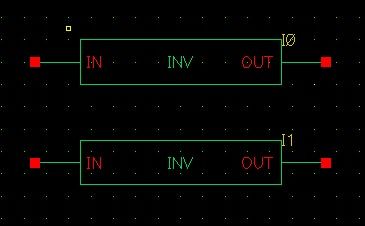

- 放置器件:從工藝廠商提供的標(biāo)準(zhǔn)單元庫(PDK)或自定義庫中,調(diào)用所需的元器件符號。例如,繪制一個反相器(Inverter),需要放置一個PMOS管、一個NMOS管和一個電源符號(VDD/VSS)。

- 電氣連線:使用連線(Wire)工具,根據(jù)電路邏輯連接各器件的端口。確保連線準(zhǔn)確無誤,這是后續(xù)仿真正確的基石。

- 添加引腳與標(biāo)簽:為電路的輸入、輸出端口添加引腳(Pin),并為內(nèi)部關(guān)鍵網(wǎng)絡(luò)添加標(biāo)簽(Label),便于仿真時識別和觀測。

- 檢查與保存:完成繪制后,使用內(nèi)置的“Check and Save”功能進行電氣規(guī)則檢查(ERC),確保沒有短路、開路或未連接端口等基礎(chǔ)錯誤。

四、 電路仿真:驗證設(shè)計功能

繪制原理圖后,必須通過仿真來驗證其功能、時序和性能是否符合預(yù)期。Cadence通常與Spectre仿真器緊密集成。

- 建立仿真環(huán)境:在原理圖界面,啟動仿真工具(如ADE L - Analog Design Environment)。需要配置仿真設(shè)置:

- 選擇仿真器:通常為Spectre。

- 添加模型庫:鏈接工藝廠商提供的晶體管模型文件(.lib或.scs),這是仿真準(zhǔn)確性的關(guān)鍵。

- 設(shè)置分析類型:

- 瞬態(tài)分析(Tran):觀察信號隨時間變化的波形,是驗證邏輯功能最常用的分析。

- 直流分析(DC):用于分析工作點、傳輸特性曲線(如反相器的電壓轉(zhuǎn)移特性VTC)。

- 交流分析(AC):分析電路的頻率響應(yīng)。

- 定義輸入激勵:為電路的輸入引腳添加激勵信號。例如,為一個反相器輸入添加一個方波時鐘(Voltage Source -> PWL或Periodic Pulse)。

- 選擇輸出信號:指定需要觀察的電路節(jié)點或輸出引腳。

- 運行仿真:執(zhí)行仿真。仿真器會根據(jù)電路網(wǎng)表、模型和激勵進行計算。

- 結(jié)果分析:在波形查看器(如WaveScan)中觀察輸出波形。驗證邏輯功能(如輸入高電平,輸出是否為低電平)、時序參數(shù)(如上升/下降時間、延遲)、功耗等指標(biāo)是否達標(biāo)。如果結(jié)果不理想,需要返回原理圖修改設(shè)計。

五、 仿真驅(qū)動的設(shè)計迭代

首次仿真往往難以達到所有設(shè)計目標(biāo)。這是一個迭代過程:

- 發(fā)現(xiàn)問題:通過仿真波形識別功能錯誤、時序違規(guī)或功耗熱點。

- 定位原因:分析是器件尺寸(如W/L比)、負(fù)載還是連接方式導(dǎo)致的問題。

- 修改原理圖:返回原理圖調(diào)整參數(shù)(如調(diào)整晶體管寬長比以改變驅(qū)動能力)或拓?fù)浣Y(jié)構(gòu)。

- 重新仿真:再次運行仿真,驗證修改效果。

反復(fù)進行“設(shè)計-仿真-優(yōu)化”的循環(huán),直到電路性能完全滿足規(guī)格書要求。這一階段的充分驗證,能為后續(xù)的版圖設(shè)計和物理實現(xiàn)掃清大量障礙。

六、 通向版圖設(shè)計

成功的原理圖與仿真是版圖設(shè)計的可靠前提。在Cadence流程中,經(jīng)過充分驗證的原理圖可以直接用于:

- 版圖生成:使用Virtuoso Layout Editor手動或借助工具(如自動布局布線工具)進行物理版圖的繪制,將每個晶體管、連線轉(zhuǎn)化為符合設(shè)計規(guī)則(DRC)的幾何圖形。

- 參數(shù)提取與后仿真:從完成的版圖中提取出包含寄生電阻、電容的實際電路網(wǎng)表,進行“后仿真”(Post-layout Simulation)。后仿真的結(jié)果會比原理圖仿真更接近芯片的實際性能,是最終簽核(Sign-off)的重要依據(jù)。

七、

掌握Cadence IC的原理圖繪制與電路仿真,是數(shù)字集成電路版圖設(shè)計之旅堅實的第一步。它不僅培養(yǎng)了工程師對電路行為的直觀理解,更建立了通過嚴(yán)謹(jǐn)?shù)姆抡鎭肀WC設(shè)計質(zhì)量的工作習(xí)慣。當(dāng)原理圖在仿真中完美運行,設(shè)計師才能充滿信心地將其轉(zhuǎn)化為精心構(gòu)筑的物理版圖,最終鑄就一顆高效、可靠的芯片。對于有志于進入IC設(shè)計領(lǐng)域的學(xué)習(xí)者,深入實踐這一過程,是邁向?qū)I(yè)殿堂的必經(jīng)之路。

如若轉(zhuǎn)載,請注明出處:http://www.cacacrc.org.cn/product/12.html

更新時間:2026-03-09 06:42:59