集成電路設計中的關鍵環節 版圖設計

集成電路設計是一個復雜而精密的系統工程,它從抽象的概念和算法出發,最終轉化為物理上可制造的硅芯片。在這一系列流程中,版圖設計扮演著至關重要的角色,是連接邏輯設計與物理實現的橋梁。

一、版圖設計的核心定位

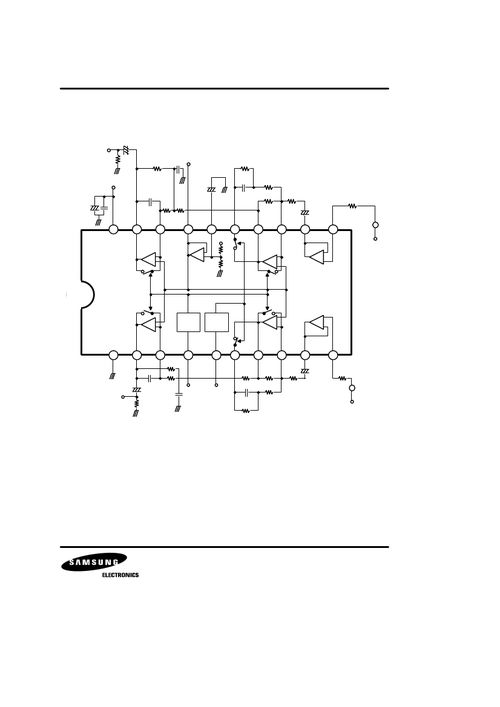

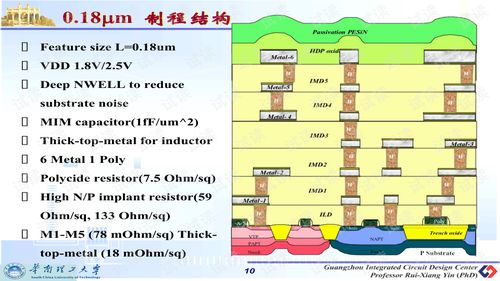

版圖設計,又稱為物理設計,是在電路邏輯設計完成之后的關鍵步驟。設計師需要將用硬件描述語言(如Verilog、VHDL)定義好的電路網表,根據特定的半導體工藝規則,轉換成一系列幾何圖形。這些圖形定義了構成芯片的每一層——如擴散層、多晶硅層、金屬互連層——的形狀、尺寸和位置。換言之,版圖就是芯片的“施工藍圖”,直接決定了芯片的性能、功耗、面積和可靠性。

二、版圖設計的主要流程與挑戰

一個典型的版圖設計流程通常包含以下幾個核心階段:

- 布局規劃:確定芯片上各個功能模塊(如存儲器、運算單元)的宏觀位置和整體芯片的形狀。目標是優化信號流、降低互連延遲并控制芯片面積。

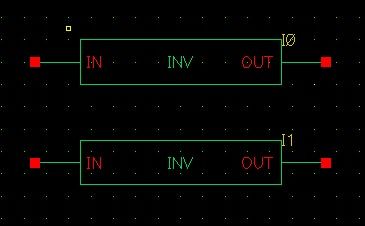

- 布圖:將標準單元和宏模塊精確地放置到芯片的規劃區域內。

- 時鐘樹綜合:構建一個均衡的時鐘分布網絡,確保時鐘信號能夠同時、低偏差地到達所有時序單元,這是保證芯片高速穩定運行的關鍵。

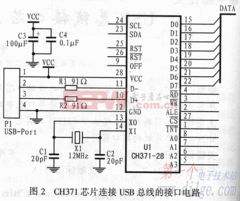

- 布線:根據電路的電氣連接關系,在多層金屬中為所有信號和電源/地線規劃并繪制出物理連線。這需要解決復雜的路徑尋找、串擾規避和通孔優化問題。

- 物理驗證:這是確保設計可制造、功能正確的最后關卡。主要包括:

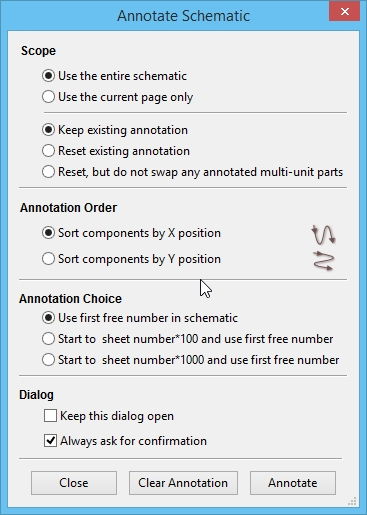

- 設計規則檢查:確保版圖完全符合晶圓代工廠的工藝制造極限(如最小線寬、間距)。

- 電路圖與版圖一致性檢查:確保物理版圖與原始電路邏輯網表在電氣連接上完全匹配。

- 電氣規則檢查:檢查天線效應、靜電放電保護等電氣可靠性問題。

整個過程中,設計師必須在性能(速度)、功耗、面積(成本)和設計周期之間進行精妙的權衡與優化。

三、先進工藝下的版圖設計新趨勢

隨著工藝節點不斷演進至7納米、5納米乃至更先進水平,版圖設計面臨著前所未有的挑戰:

- 物理效應加劇:短溝道效應、線電阻/電容增大、電源電壓降低等,使得時序收斂和功耗控制變得極其困難。

- 設計規則復雜化:多重曝光、自對準多重圖案等新技術帶來了極其復雜和限制性的設計規則。

- 對EDA工具的深度依賴:完全依賴手工設計已不現實,自動化布局布線工具、簽核分析工具的作用愈發核心。

因此,現代版圖設計不僅是“繪圖”工作,更需要設計師深刻理解器件物理、工藝制程和電路原理,并與EDA工具進行高效互動,采用如模塊化設計、層次化設計等策略來管理復雜度。

###

集成電路版圖設計是想象力與精密工程的交匯點。它將無形的電子思想,塑造成有形的、功能強大的硅基實體。在摩爾定律持續推進的今天,優秀的版圖設計是釋放先進工藝潛力、實現高性能、低功耗芯片不可或缺的基石。掌握其原理與藝術,是每一位集成電路設計工程師通向卓越的必經之路。

如若轉載,請注明出處:http://www.cacacrc.org.cn/product/1.html

更新時間:2026-03-09 16:19:01